Hardware – Comparing 10G SFP+ with XFP

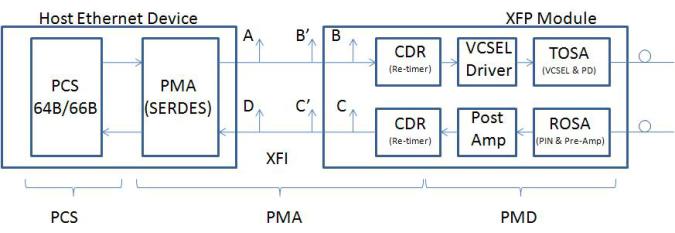

In the last post I discussed clock and data recovery (CDR). This post examines an application of re-timers (or CDRs) within XFP and SFP+ transceivers. I’ve previously covered the size, power and connector differences of 10G transceivers before, but this post will focus on the differences between XFP and SFP+ and how they connect to the ASIC. Take a look at the XFP block digram below which shows the XFI electrical interface from an XFP module connecting to the the host device (ASIC…